09 January 2024

Binary LMC simulator (Little Man Computer)

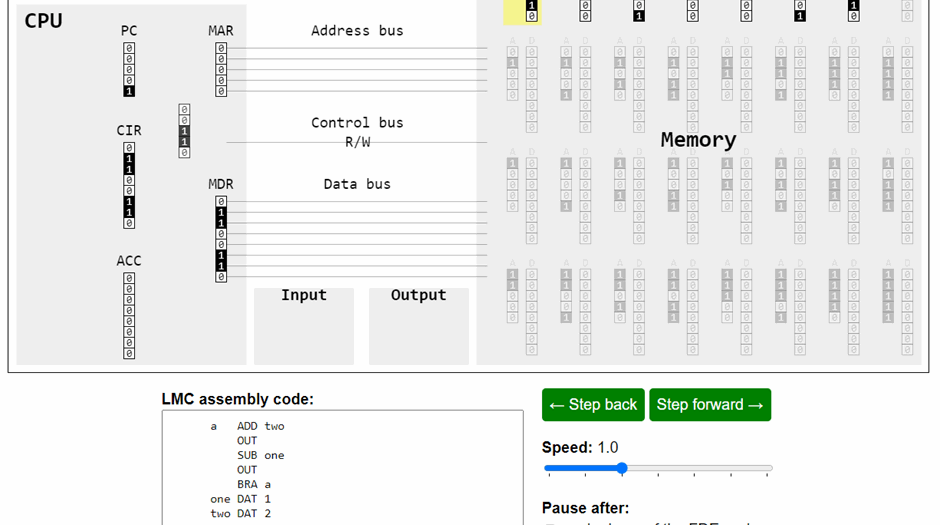

I’ve made a visual LMC simulator that uses binary rather than denary - Binary LMC simulator . This will be particularly useful for teachers/students doing OCR A-level computer science.

To help with the OCR curriculum, the simulator uses PC, CIR, ACC, MAR and MDR registers and has clear address, data and control buses. It's built around the FDE (fetch-decode-execute) cycle.

Some useful features:

- animates the bits flowing around

- user-controllable speed

- explains each stage of the FDE cycle in detail

- allows stepping forward/back an FDE stage

- allows pausing after an FDE cycle or stage

- click to pause/play at any time

As an A-level computer science teacher, I used this with my class a few months ago with a lot of success. It really helped them to understand the FDE cycle better as well as LMC, opcode vs operand etc. They wrote their own simple LMC assembly-code programs using it.

The simulator uses a 5bit address bus and 8bit data bus. This gives 32 addressable memory locations holding 8bits each. This is more than enough for simple LMC programs, but is clearly more limited than the usual 100 addresses. It supports all 11 LMC instructions. It doesn’t yet work with negative integers, other than to set a 1 as the MSB for negative numbers. I intend to implement 2s-complement between -128 and +127 soon.

Discussion

Please login to post a comment